# International Journal of Engineering

Journal Homepage: www.ije.ir

An Accurate 2D Analytical Model for Transconductance to Drain Current ratio  $(g_m/I_d)$  for a Dual Halo Dual Dielectric Triple Material Cylindrical Gate All Around MOSFET

N. Gupta\*, J. K. B Patel, A. K. Raghav

Amity University Haryana, Gurugram, India

#### PAPER INFO

Paper history: Received 13 November 2017 Received in revised form 17 February 2018 Accepted 09 March 2018

Keywords: Short Channel Effects Triple Metal Dual Dielectric material Halo Implant Transconductance

## ABSTRACT

A dual-halo dual-dielectric triple-material cylindrical-gate-all-around/surrounding gate (DH-DD-TM-CGAA/SG) MOSFET has been proposed and an analytical model for the transconductance-to-drain current ratio (TDCR) has been developed. It is verified that incorporation of dual-halo with dual-dielectric and triple-material results in enhancing the device performance in terms of improved TDCR. The effect on TDCR is analyzed for variations in device parameters like oxide thickness, silicon thickness, channel doping concentration, channel length and drain bias. The results show that larger value of  $g_{\rm m}/I_{\rm d}$  can be obtained in proposed device in comparison to other existing triple material structures which makes it suitable for micropower applications. The analytical results of the developed  $g_{\rm m}/I_{\rm d}$  model strongly agrees with the simulated results obtained from TCAD Silvaco.

doi: 10.5829/ije.2018.31.07a.05

### NOMENCLATURE

| $\overline{q}$   | Electronic charge                     | $t_{oxeffdh}$               | Oxide thickness (nm)        |

|------------------|---------------------------------------|-----------------------------|-----------------------------|

| $N_{ak}$         | Acceptor ion concentration (atoms/m³) | Greek Symbols               |                             |

| $C_{_{oxeffdh}}$ | Oxide capacitance (F)                 | $\phi_k(r,z)$               | Surface Potential (V)       |

| R                | Radius of silicon pillar (nm)         | $oldsymbol{arepsilon}_{Si}$ | Permitivity of silicon      |

| ${ m V}_{fbk}$   | Flat-band voltage (V)                 | $oldsymbol{\phi}_{mk}$      | Work function of metal (eV) |

| $E_{_g}$         | Energy band gap (eV)                  | $\chi_s$                    | Elecron affinity (eV)       |

| $g_m$            | Transconductance (mho)                | $oldsymbol{\phi}_{fp}$      | Fermi potential (eV)        |

# 1. INTRODUCTION

At present conventional MOSFET has reached its scaling limit due to the presence of short channel effects and hence has degraded the device performance. So future generation devices require new device structures with new materials to accelerate the performance of device in nanoregime. The TM-SG MOSFET is the

most popular device as compared to the planar MOSFETs [1]. Higher current driving capability, enhanced immunity against short channel effects, higher reliability and increased device packing density have been reported by many authors on this device [2, 3]. TDCR is a key metric to access the performance of a device instead of transconductance which is also known as the quality factor of a MOSFET device [4]. This ratio for the MOSFET device means the amplification produced by the device to power dissipated through drain current. The higher value of TDCR will give

Please cite this article as: N. Gupta, J. K. B Patel, A. K. Raghav, An Accurate 2D Analytical Model for Transconductance to Drain Current ratio  $(g_m/I_d)$  for a Dual Halo Dual Dielectric Triple Material Cylindrical Gate All Around MOSFETs, International Journal of Engineering (IJE), IJE TRANSACTIONS A: Basics Vol. 31, No. 7, (July 2018) 1038-1043

<sup>\*</sup>Corresponding Author Email: <a href="mailto:neerajsingla007@gmail.com">neerajsingla007@gmail.com</a> (N. Gupta)

highest voltage gain of a MOSFET device which is necessary for analog/RF applications and also useful for designing of memory circuits [5, 6].

The surface potential technique to find the TDCR and body factor (n) of fully depleted double-gate SOI MOSFETs is presented by Rajendran et al. [7]. Kranti et al. [8] have sucessfully applied the analytical model to enhance the TDCR (g<sub>m</sub>/I<sub>d</sub>) of a vertical surrounding gate MOSFET. But this model cannot be applied to triple material surrounding gate devices. Balamurgan et al. [9] have proposed a TDCR model for DM-SG MOSFET. Ghosh et al. [10] developed a model for dual material dual dielectric CGAA MOSFET. But not useful for triple material dual dielectric MOSFETs. Wang et al. [11] have proposed a new structure known as TM-SG MOSFET in which the surface potential model was developed using superposition method. But the method comprises of complex mathematical equations. Recently a model was reported by Dhanaselvam et al. [12] for Triple material surrounding gate MOSFETs. The solution of Poisson equation gives TDCR. No work has yet been reported on the g<sub>m</sub>/I<sub>d</sub> ratio for DH-DD-TM-CGAA MOSFET.

In this paper, analytical model of TDCR is presented. The TDCR of proposed device is calculated by taking the derivative of minimum surface potential. Furthermore the effet of variation in device parameters like oxide thickness, channel length anddrain bias are also studied. The result revals that proposed device have more TDCR in comparison to existing TM-SG MOSFETs. The analytical results have been validated by simulated results with the help of TCAD Silvaco. Therefore, device geometry is a key parameter for designing of future VLSI circuits.

# 2. DEVICE STRUCTURE

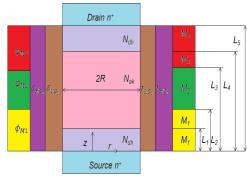

Figure 1 shows the schematic diagram of DH-DD-TM-CGAA MOSFET structure.

**Figure 1.** Cross sectional schematic of dual-halo dual-dielectric triple-material cylindrical-gate—all-around (DH-DD-TM-CGAA) MOSFET

Figure 1 shows that the gate terminal consists of three metals with different work functions for cylindrical surrounding gate MOSFET [13]. In this Triple metal gate schematic, the symmetric dual halo doping is incorporated for the first time along with dual dielectric to form a novel device structure. The lengths  $L_1$  and  $L_5$ – $L_4$  are halo doped with concentration  $N_{dh}$  while the rest of the regions are doped with acceptor doping concentration  $N_{ak}$ , assuming that  $N_{dh}$  is greater than  $N_{ak}$  [14].

The cylindrical coordinate system is a radial direction r, an angular direction  $\theta$  in the radial plane, and a vertical direction z, as shown in Figure 1. The quantum effects are neglected in the present analysis as the device diameter and channel length is not below 10 and 30 nm, respectively [15].

The potential distribution in the channel can be expressed by the Poisson's equation [16] and can be written as:

$$\begin{split} &\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial \left[\phi_{k}(r,z)\right]}{\partial r}\right) + \frac{\partial^{2}\left[\phi_{k}(r,z)\right]}{\partial z^{2}} \\ &= \frac{qN_{ak}}{\varepsilon_{Si}}\left(L_{k-1} \leq z \leq L_{k}\right) \end{split} \tag{1}$$

where, k=1, 2, 3, 4, 5

The total potential for the entire channel length can be defined as:

$$\phi(r,z) = \begin{cases} \phi_1(r,z); 0 \le z \le L_1 \\ \phi_2(r,z); L_1 \le z \le L_2 \\ \phi_3(r,z); L_2 \le z \le L_3 \\ \phi_4(r,z); L_3 \le z \le L_4 \\ \phi_5(r,z); L_4 \le z \le L_5 \end{cases}$$

(2)

The potential distribution is approximated using parabolic profile for DH-DD-TM-CGAA MOSFET in the radial direction and is given by literature [10].

$$\phi(r,z) = \zeta_0(z) + \zeta_1(z)r + \zeta_2(z)r^2$$

(3)

Were, the constant  $\zeta_0(z)$ ,  $\zeta_1(z)$  and  $\zeta_2(z)$  can be obtained by substituting conditions at the boundary.

For obtaining surface potential, the corresponding boundary conditions are also reported in literature [17]: Using the boundary condition equations, in the surface potential Equation (3) and then substituting in Equation (1). Surface potential is expressed as follows:

$$\frac{d^{2}\phi_{s}(z)}{dz^{2}} - \phi_{s}(z) \left(\frac{2C_{\text{oxeffdh}}}{\varepsilon_{Si}R}\right) + (v_{gs} - v_{fbk}) \left(\frac{2C_{\text{oxeffdh}}}{\varepsilon_{Si}R}\right) = \frac{qN_{ak}}{\varepsilon_{Si}}$$

(4)

$$\frac{d^2\phi_s(z)}{dz^2} - \kappa^2\phi_s(z) = \chi \tag{5}$$

$$\kappa^2 = \frac{2C_{oxeffdh}}{\varepsilon_{Si}R}, \chi = \frac{qN_{ak}}{\varepsilon_{Si}} - \kappa^2(v_{gs} - v_{fbk})$$

(6)

where, k=1, 2, 3, 4, 5

$$\mathbf{v}_{fbj} = \phi_{mj} - \left\{ \chi_s + E_g - q\phi_{fp} \right\}$$

where  $j = 1, 2, 3, 4, 5$

The solution of second order differential Equation (5), through the complementary and the particular integral functions is given as:

$$\phi_{sk}(z) = \alpha_k e^{(\kappa z)} + \beta_k e^{(-\kappa z)} - \frac{\chi_k}{\kappa^2} \qquad l_{k-1} \le z \le l_k$$

$$M_k = \frac{\chi_k}{\kappa^2}, \delta_k = \exp(\kappa L_k), \delta_k^{-1} = \exp(-\kappa L_k)$$

(8)

where,  $\alpha_k \& \beta_k$  are arbitrary constants, which are calculated with the help of continuity conditions for the surface potential distribution  $(\phi)$  and the field distribution (E) at the interfaces of different metal gates. For the value of  $\alpha_k \& \beta_k$  reported in literature [17].

The minimum surface potential is obtained by differentiating surface potential Equation (5) relative to the direction z and making it zero for getting the minimum surface potential  $\phi_{\text{clumin}}$ .

$$\phi_{\text{slmin}} = 2\sqrt{\alpha_1 \beta_1} - \frac{\chi_1}{\kappa^2} \tag{9}$$

The TDCR is a measure of the efficiency of the device. Hence it is also known as Transconductance generation efficiency or Transconductance generation factor. It is inversely proportional to thermal voltage. The expression for TDCR is given as:

$$\frac{g_m}{I_{ds}} = \frac{q}{k_B T} \left( \frac{\partial \left( 2\sqrt{\alpha_1 \beta_1} - \frac{\chi_1}{\kappa^2} \right)}{\partial V_{gs}} \right)$$

(10)

# 3. RESULTS AND DISCUSSION

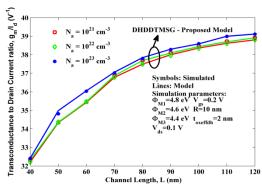

In order to scrutinize the effectiveness of the proposed model, the DH-DD-TM-SG and TM-SG MOSFETs devices were studied, compared and results are presented. Further, the DH-DD-TM-SG device outcomes were compared with the simulated results of ATLAS 3D device simulator. The simulation parameters for TDCR model analysis are: R=10nm,  $V_{\rm gs}{=}0.2V,\,t_{\rm oxeffdh}{=}2{\rm nm}.$  The work function of metal gate at the source end is 4.8 eV (Au) and work function of metal gate at the drain end is 4.4 eV (Ti).

The TDCR is plotted with respect to the position along the channel length for diverse values of channel doping concentration are depicted in Figure 2. The increase in TDCR is observed with increase in the channel doping concentration. It is obvious from the figure that, larger the channel doping concentration more is the  $g_m/I_d$  ratio at a specific channel length. The analytical results are plotted and validated with simulated results obtained from TCAD Silvaco [18].

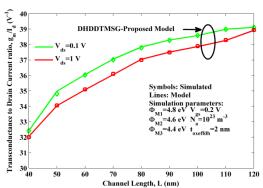

In Figure 3, the TDCR is plotted with respect to position along the channel length at different radius of silicon pillar. As the radius of silicon pillar increases, the  $g_m/I_d$  ratio decreases. It is observed from the figure that DH-DD-TM-CGAA MOSFET having higher  $g_m/I_d$  ratio at  $R\!=\!10\text{nm}.$  The analytical results have been compared with the simulated results using TCAD Silvaco and an excellent agreement was achieved between the two.

Figure 4 shows the variation in TDCR as a function of the position along the channel length at different drain bias. As channel length increases,  $g_m/I_d$  approaches its ideal value of q/KT, whereas for shorter lengths influence of short channel effects (SCEs) is more and  $g_m/I_d$  decreases significantly.

**Figure 2.** TDCR with varying channel length at different doping concentration

**Figure 3.** TDCR with varying channel length at different radius of silicon pillar

**Figure 4.** TDCR as a function of the position along the channel length at different drain bias for DH-DD-TM-CGAA MOSFET

It is also depicted in the figure that more value of  $g_m/I_d$  is achieved at lower value of  $V_{ds}$ . The abrupt reduction in  $g_m/I_d$  ratio at a particular value of channel length shows the starting of SCEs. The  $g_m/I_d$  decreases with the increase in drain bias and it is due to drain induced barrier lowering known as short channel effects. The DH-DD-TM-CGAA MOSFET have higher  $g_m/I_d$  at particular drain bias. The analytical results are plotted and validated with simulation result obtained from TCAD Silvaco.

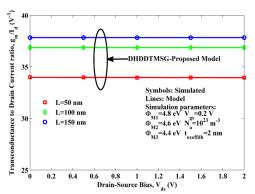

Figure 5 shows the curve between the  $g_m/I_d$  ratio based on the drain bias for DH-DD-TM-SG MOSFETs for various values of channel length. There is smaller value of  $g_m/I_d$  at higher values of drain bias. This is mainly due to the punch through as a result of large electric field near the drain. It is observed from the figure that as the value of channel length increases, the  $g_m/I_d$  value also increases. So DH-DD-TM-CGAA MOSFETs will be more beneficial for analog circuit applications. The analytical results are well correlated with the simulation results proving the accuracy of proposed model.

**Figure 5.** TDCR as a function of the drain source bias at different channel length for DH-DD-TM-CGAA MOSFET

# 4. COMPARISION of DH-DD-TM-SG and TM-SG

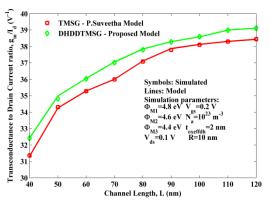

The TDCR of DH-DD-TM-SG MOSFET is estimated for different lengths along the channel. Figure 6 shows the TDCR of proposed device and TM-SG with channel length. The triple metal/material surrounding gate MOSFET is used for making comparative analysis with the proposed model. Since the TM-SG MOSFET uses similar approach to find out the TDCR, so it is used for comparison. As obvious from Figure 6 as well as from the Table 1 that DH-DD-TM-CGAA MOSFET provides higher value of TDCR than the TM-SG MOSFET. The g<sub>m</sub>/I<sub>d</sub> ratio will be increased whenever there will be an incremental change in the channel length. Moreover it is clearly visible from the figure that due to the presence of SCEs [19], there is significant reduction in the g<sub>m</sub>/I<sub>d</sub> ratio at lower channel lengths. Hence the DH-DD-TM-CGAA MOSFETs can be used in micro power circuit applications where higher TDCR is essential.

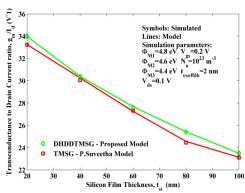

Figure 7 shows the dependence of  $g_m/I_d$  ratio on varying silicon film thickness at an appropriate channel length for DH-DD-TM-CGAA and TM-SG MOSFETs. As evident from Figure 7 and Table 2, it can be concluded that the DH-DD-TM-SG MOSFET shows a peak  $g_m/I_d$  ratio  $34V^{-1}$ whereas TM-SG attain  $33.1V^{-1}$  at  $t_{si}$ =20nm. The ratio decreases with respect to increase in silicon film thickness. The simulated results are compared with analytical results and close agreement is obtained.

**Figure 6.** TDCR of TMDDCGAA and DH-DD-TM-CGAA MOSFET at various channel length

**TABLE 1.** G<sub>m</sub>/I<sub>d</sub> values at different channel length

| I (nm) | $G_m/I_d$ (V <sup>-1</sup> ) |             |  |

|--------|------------------------------|-------------|--|

| L (nm) | TM-SG                        | DH-DD-TM-SG |  |

| 40     | 31.35                        | 32.41       |  |

| 60     | 35.27                        | 36.03       |  |

| 80     | 37.08                        | 37.79       |  |

| 100    | 38.09                        | 38.59       |  |

| 120    | 38.44                        | 39.01       |  |

**Figure 7.** TDCR on varying silicon film thickness for DH-DD-TM-CGAA and TM-SG MOSFET

**TABLE 2.**G<sub>m</sub>/I<sub>d</sub> values for different Silicon thickness

| T. ()         | $G_m/I_d$ (V <sup>-1</sup> ) |             |  |

|---------------|------------------------------|-------------|--|

| $T_{si}$ (nm) | TM-SG                        | DH-DD-TM-SG |  |

| 20            | 33.13                        | 34.00       |  |

| 40            | 30.05                        | 30.38       |  |

| 60            | 27.31                        | 27.59       |  |

| 80            | 24.45                        | 25.37       |  |

| 100           | 23.10                        | 23.50       |  |

# 5. CONCLUSIONS

In this paper, an accurate 2-D analytical model for g<sub>m</sub>/I<sub>d</sub> ratio of the novel device DH-DD-TM-SG MOSFET has been presented and scrutinized. The small signal MOSFET model, which is mandatory to determine the frequency behavior, is beyond the scope of present analysis. The study was then continued to obtain higher g<sub>m</sub>/I<sub>d</sub> values for all combination of device parameters. Further, the TDCR model of proposed device has been compared with the TM-SG strucure. The g<sub>m</sub>/I<sub>d</sub> value of DH-DD-TM-SG MOSFETs does not fall down at smaller channel lengths and larger silicon film thickness unlike that of TM-SG MOSFETS. The higher g<sub>m</sub>/I<sub>d</sub> ratio of DH-DD-TM-SG MOSFETs is beneficial for designing of analog circuits. Therefore it is concluded that the g<sub>m</sub>/I<sub>d</sub> ratio could be intensified by integrating the dual halo with dual dielectric instead of TM-SG MOSFETs design.

# 6. REFERENCES

- Park, J.-T. and Colinge, J.-P., "Multiple-gate soi mosfets: Device design guidelines", *IEEE Transactions on Electron Devices*, Vol. 49, No. 12, (2002), 2222-2229.

- Kumar, M.J., Orouji, A.A. and Dhakad, H., "New dual-material surrounding gate nanoscale mosfet: Analytical threshold-voltage

- model", *IEEE Transactionson Electron Devices*, Vol. 53, No. 4, (2006), 920-923.

- Chiang, T., Chen, M. and Wang, H., "A new two-dimensional model for dual material surrounding-gate (DMSG) mosfet's", in Electron Devices and Solid-State Circuits, 2007. EDSSC 2007. IEEE Conference on, IEEE. (2007), 597-600.

- Balamurugan, N., Sankaranarayanan, K. and John, M.F., "2d transconductance to drain current ratio modeling of dual material surrounding gate nanoscale soi mosfets", *Journal of Semiconductor Technology and Science*, Vol. 9, No. 2, (2009), 110-116.

- Niaraki, R. and Nobakht, M., "A sub-threshold 9t static randomaccess memory cell with high write and read ability with bit interleaving capability", *International Journal of Engineering-Transactions B: Applications*, Vol. 29, No. 5, (2016), 630-636.

- Karimi, G. and Shirazi, S., "Ballistic (n, 0) carbon nanotube field effect transistors' iv characteristics: A comparison of n= 3a+ 1 and n= 3a+ 2", *International Journal of Engineering-Transactions A: Basics*, Vol. 30, No. 4, (2017), 516-522.

- Rajendran, K. and Samudra, G., "Modelling of transconductance-to-current ratio (g<sub>m</sub>/I<sub>d</sub>) analysis on double-gate soi mosfets", *Semiconductor Science and Technology*, Vol. 15, No. 2, (2000), 139-144.

- Kranti, A., Haldar, S. and Gupta, R., "Design and optimization of vertical surrounding gate mosfets for enhanced transconductance-to-current ratio (g<sub>m</sub>/I<sub>ds</sub>)", Solid-State Electronics, Vol. 47, No. 1, (2003), 155-159.

- Balamurugan, N., Sankaranarayanan, K., Amutha, P. and John, M.F., "An analytical modeling of threshold voltage and subthreshold swing on dual material surrounding gate nanoscale mosfets for high speed wireless communication", JSTS: Journal of Semiconductor Technology and Science, Vol. 8, No. 3, (2008), 221-226.

- Ghosh, P., Haldar, S., Gupta, R. and Gupta, M., "Analytical modeling and simulation for dual metal gate stack architecture (DMGSA) cylindrical/surrounded gate mosfet", *JSTS: Journal* of Semiconductor Technology and Science, Vol. 12, No. 4, (2012), 458-466.

- Wang, H.-K., Wu, S., Chiang, T.-K. and Lee, M.-S., "A new two-dimensional analytical threshold voltage model for shortchannel triple-material surrounding-gate metal-oxidesemiconductor field-effect transistors", *Japanese Journal of Applied Physics*, Vol. 51, No. 5R, (2012), 1-5.

- Dhanaselvam, P.S., Balamurugan, N. and Ramakrishnan, V., "A 2d transconductance and sub-threshold behavior model for triple material surrounding gate (TMSG) mosfets", *Microelectronics Journal*, Vol. 44, No. 12, (2013), 1159-1164.

- Dubey, S., Santra, A., Saramekala, G., Kumar, M. and Tiwari, P.K., "An analytical threshold voltage model for triple-material cylindrical gate-all-around (TM-CGAA) mosfets", *IEEE Transactions on Nanotechnology*, Vol. 12, No. 5, (2013), 766-774.

- Dhanaselvam, P.S., Balamurugan, N., Chakaravarthi, G.V., Ramesh, R. and Kumar, B.S., "A 2d analytical modeling of single halo triple material surrounding gate (SHTMSG) mosfet", *Journal of Electrical Engineering & Technology*, Vol. 9, No. 4, (2014), 1355-1359.

- Naveh, Y. and Likharev, K., "Modeling of 10-nm-scale ballistic mosfet's", *IEEE Electron Device Letters*, Vol. 21, No. 5, (2000), 242-244.

- Sharifi, M. and Adibi, A., "Semiconductor device simulation by a new method of solving poisson, laplace and schrodinger equations", *International Journal of Engineering*, Vol. 13, No. 1, (2000), 89-94.

- Gupta, N., Patel, J.K.B. and Raghav, A.K., "Modeling and analysis of threshold voltage for dual-halo dual-dielectric triplematerial surrounding-gate mosfets", *International Journal of Pure and Applied Mathematics*, Vol. 118, No. 18, (2018), 3759-3771.

- Atlas, D.S., "Atlas user's manual", Silvaco International Software, Santa Clara, CA, USA, (2005).

- Shafiabadi, M. and Mehrabani, Y.S., "Symmetrical, low-power, and high-speed 1-bit full adder cells using 32nm carbon nanotube field-effect transistors technology", *International Journal of Engineering-Transactions A: Basics*, Vol. 28, No. 10, (2015), 1447-1454.

# An Accurate 2D Analytical Model for Transconductance to Drain Current ratio $(g_m/I_d)$ for a Dual Halo Dual Dielectric Triple Material Cylindrical Gate All Around MOSFET

N. Gupta, J. K. B Patel, A. K. Raghav

Amity University Haryana, Gurugram, India

PAPER INFO

Paper history: Received 13 November 2017 Received in revised form 17 February 2018 Accepted 09 March 2018

Keywords: Short Channel Effects Triple Metal Dual Dielectric material Halo Implant Transconductance dual-hialo-gate-all-around / gateway (DH- یک دیود الکترومغناطیسی سه گانه -MOSFET به به MOSFET بیشنهاد شده است و یک مدل تحلیلی برای نسبت جریان فعلی به تخلیه (DD-TM-CGAA / SG TDCR) پیشنهاد شده است و یک مدل تحلیلی برای نسبت جریان فعلی به تخلیه (DD-TM-CGAA / SG TDCR) داده شده است. ترکیب دوگانه با مواد دو الکتریکی و سه بعدی موجب افزایش عملکرد دستگاه از لحاظ بهبود doping می شود. در اثر TDCR برای تغییرات در پارامترهای دستگاه مانند ضخامت اکسید، ضخامت سیلیکون، غلظت gm/  $I_{\rm d}$  کانال، طول کانال و تخریب تخلیه تجزیه و تحلیل شده است. نتایج نشان می دهد که مقدار بزرگتر از  $g_{\rm m}/I_{\rm d}$  در دستگاه پیشنهادی در مقایسه با سایر سه گانه موجود ساختارهای مادی است که آن را برای برنامه های کاربردی میکرودرمی مناسب می سازد. نتایج تحلیلی مدل  $g_{\rm m}/I_{\rm d}$  توسعه یافته به شدت با نتایج شبیه سازی شده از TCAD Silvaco موافق

doi: 10.5829/ije.2018.31.07a.05