International Journal of Computer Engineering and Technology (IJCET) Volume 16, Issue 1, Jan-Feb 2025, pp. 3987-4016, Article ID: IJCET\_16\_01\_274 Available online at https://iaeme.com/Home/issue/IJCET?Volume=16&Issue=1 ISSN Print: 0976-6367; ISSN Online: 0976-6375; Journal ID: 5751-5249 Impact Factor (2025): 30.78 (Based on Google Scholar Citation) DOI: https://doi.org/10.34218/IJCET\_16\_01\_274

# PCIE VERIFICATION AT HIGH SPEEDS: CHALLENGES, SOLUTIONS, AND FUTURE

### TRENDS

**Deepak Kumar Lnu** Principal Engineer, USA.

## PCIe Verification at High Speeds: Challenges, Solutions, and Future Trends

### ABSTRACT

PCI Express (PCIe) technology is a cornerstone of high-speed data transfer, driving innovation across numerous modern applications. This article delves into the increasingly complex landscape of PCIe verification, specifically addressing the unique challenges presented by advanced features in PCIe 6.0 and PCIe 7.0, such as Pulse

https://iaeme.com/Home/journal/IJCET

Amplitude Modulation 4 (PAM4) signaling, Flow Control Units (FLITs), Forward Error Correction (FEC), and intricate power management states like L0p. We examine the critical aspects of protocol verification, signal integrity validation, and system-level integration, highlighting the growing difficulties in ensuring reliable operation at unprecedented data rates. To tackle these challenges, this paper presents comprehensive solutions, including advanced verification methodologies, error injection techniques, and the strategic application of artificial intelligence and machine learning (AI/ML) to automate and optimize verification processes. Furthermore, the article explores the implications of PCIe verification in critical domains such as highperformance computing, automotive systems, and large-scale data centers, emphasizing the necessity of robust verification frameworks to ensure stable and efficient operation. Looking to the future, we discuss the transformative potential of AI/ML, which is poised to revolutionize PCIe verification, enabling more efficient and thorough validation of increasingly complex systems. This paper aims to provide valuable insights and practical guidance for engineers and researchers working in high-speed interconnect verification.

**Keywords:** PCIe Verification, PAM4, FLITS, FEC, L0p, Signal Integrity, Artificial Intelligence, Automotive Safety, High-Performance Computing

**Cite this Article:** Deepak Kumar Lnu. (2025). PCIe Verification at High Speeds: Challenges, Solutions, and Future Trends. *International Journal of Computer Engineering and Technology (IJCET)*, 16(1), 3987-4016.

$https://iaeme.com/MasterAdmin/Journal_uploads/IJCET/VOLUME\_16\_ISSUE\_1/IJCET\_16\_01\_274.pdf$

#### **1. Introduction**

In high-speed data transmission, PCI Express (PCIe) has become the ubiquitous standard, powering the backbone of modern computing, networking, and AI-driven applications. The market trajectory underscores this dominance, with projections indicating extraordinary growth of USD 53.74 billion from 2024-2028, driven by seamless integration with IEEE 1394 (FireWire) protocols and the transformative role of artificial intelligence in market dynamics [1]. This substantial market expansion reflects the increasing adoption of PCIe across diverse computing platforms and emphasizes the critical need for robust verification methodologies.

#### Deepak Kumar Lnu

The rapid advancement of PCIe technology, aimed at meeting the ever-increasing bandwidth and low latency demands, has introduced a corresponding surge in verification complexity. This complexity is particularly evident in developing next-generation PCIe 7.0 interfaces, where the industry has responded with groundbreaking verification solutions. Introducing the industry's first Verification IP for PCIe 7.0 in June 2024 marks a significant milestone in addressing these challenges, providing comprehensive coverage for exhaustive protocol, methodology, verification, and configuration testing requirements [2].

Each layer of the PCIe architecture, from the transaction to the physical layer, requires meticulous scrutiny to validate its functionality and performance under diverse operating conditions. The verification landscape has been further transformed by integrating artificial intelligence and machine learning capabilities, which are revolutionizing traditional testing methodologies [1]. These advanced technologies enable more efficient verification processes while ensuring thorough coverage of the complex protocol requirements.

Introducing new features, such as advanced signaling techniques, error correction mechanisms, and complex power management states, has amplified these verification challenges. The rapid pace of technological advancement, evidenced by the quick progression from PCIe 6.0 to PCIe 7.0, necessitates increasingly sophisticated verification approaches to ensure robust system performance [2]. As we delve into the intricacies of PCIe verification, the role of innovative methodologies becomes increasingly critical in maintaining system reliability.

The imperative to maintain high reliability is particularly acute in domains like data centers, automotive systems, and high-performance computing, where system failures can have severe consequences. This reliability requirement, coupled with the projected market growth to 2028 [1], underscores the critical importance of comprehensive verification strategies in ensuring the successful deployment of PCIe technology across these vital sectors.

#### 2. Technical Evolution: PCIe Gen6/Gen7 Breakthroughs

The evolution of PCIe technology has reached new heights with remarkable advancements in data transmission capabilities. According to Mangla's comprehensive research on PCIe evolution, the technology has demonstrated an extraordinary progression from its initial Gen1 transfer rates of 2.5 GT/s through successive generations. This systematic advancement has established a consistent pattern of doubled bandwidth capabilities with each new generation, culminating in the revolutionary achievements of Gen6 and Gen7

implementations. The research particularly emphasizes how this evolutionary path has maintained backward compatibility while pushing the boundaries of data transfer speeds [3].

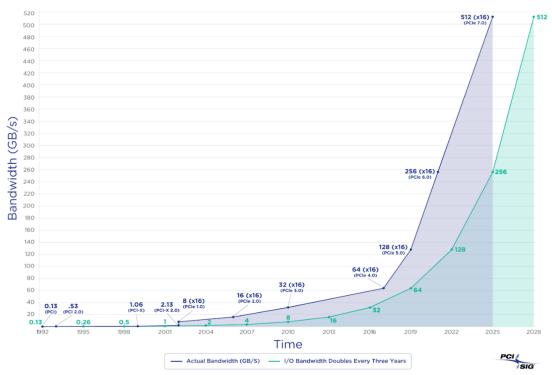

The latest milestone in PCIe development is marked by PCIe 7.0, which delivers groundbreaking data rates of 128.0 GT/s per lane, effectively doubling the performance of its predecessor, PCIe 6.0 (64.0 GT/s). Synopsys' recent technical analysis confirms that this enhancement enables an x16 link configuration to achieve a remarkable bi-directional bandwidth of up to 512 GB/s. This significant improvement has been made possible through sophisticated verification methodologies, including the industry's first Verification IP for PCIe 7.0, which provides comprehensive coverage for exhaustive protocol testing. The advancement is particularly crucial for supporting emerging applications in artificial intelligence, machine learning, and high-performance computing (HPC) domains, where data throughput requirements continue to escalate [2].

Fig. 1: PCIe Bandwidth Evolution Timeline (2003-2028) - Historical Growth and Future Projections

The advancement in PCIe technology represents a convergence of multiple innovative features that enable unprecedented performance. The transition from NRZ encoding to PAM4 signaling has revolutionized data transmission efficiency, doubling the data rate per clock cycle while maintaining signal integrity at higher frequencies. This development, coupled with implementing Flow Control Units (FLITs), has fundamentally transformed data transfer processes. The integration of Forward Error Correction (FEC) algorithms has remarkably improved error resilience, with bit error rates being reduced from 10<sup>-6</sup> to 10<sup>-15</sup>, establishing new standards for data reliability in high-speed communications. Complementing these advancements, introducing the L0p low-power state has addressed the critical challenge of power efficiency during active operations, ensuring optimal performance while minimizing energy consumption [2].

The table below compares PCIe Gen5, Gen6, and Gen7, highlighting their key advancements and distinctions [4].

| Feature                 | PCIe Gen5                         | PCIe Gen6                                             | PCIe Gen7                                   |

|-------------------------|-----------------------------------|-------------------------------------------------------|---------------------------------------------|

| Data Rate per Lane      | 32.0 GT/s                         | 64.0 GT/s (2x Gen 5)                                  | 128.0 GT/s (2x Gen6)                        |

| Bandwidth (x16)         | Up to 128 GB/s bi-<br>directional | Up to 256 GB/s bi-<br>directional (2x Gen5)           | Up to 512 GB/s bi-<br>directional (2x Gen6) |

| Signaling<br>Technology | NRZ (Non-Return to<br>Zero)       | PAM4 (Pulse<br>Amplitude Modulation<br>with 4 levels) | PAM4                                        |

| Encoding                | 128b/130b                         | FLIT-based (256-byte fixed-size packets)              | FLIT-based                                  |

| Error Correction        | Basic CRC                         | Forward Error<br>Correction (FEC) +<br>CRC            | Enhanced FEC + CRC                          |

| Power Efficiency        | Basic                             | Introduced L0p low-<br>power state for scaling        | Further optimized over<br>Gen 6             |

| Table 1:  | PCIe Gen5, | Gen6, and | Gen7 Com | narison |

|-----------|------------|-----------|----------|---------|

| 1 4010 1. |            | Geno, and | Geni Com | parison |

| Security<br>Enhancements  | None                                     | CMA, IDE                                 | Advanced CMA, IDE                                    |

|---------------------------|------------------------------------------|------------------------------------------|------------------------------------------------------|

| Target<br>Applications    | AI/ML, HPC, high-<br>performance storage | Advanced AI, 800G<br>Ethernet, NVMe, CXL | 800G Ethernet, quantum<br>computing, next-gen<br>HPC |

| Release Timeline          | 2019                                     | 2021                                     | Expected 2025                                        |

| Backward<br>Compatibility | Full compatibility with earlier gens     | Full compatibility with earlier gens     | Full compatibility with earlier gens                 |

#### 3. Key Challenges in Verifying High-Speed PCIe Implementations

The advancement of PCIe technology introduces significant verification and implementation challenges that require innovative solutions. Here's a detailed analysis of key challenge areas:

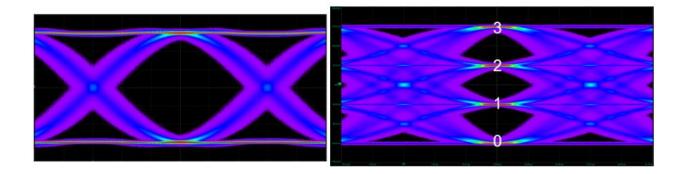

#### **Challenges with PAM4 Signaling**

PAM4 signaling, while doubling data rates, introduces several challenges, as also revealed in Teledyne LeCroy's research PCI Express 6.0 adds multilevel PAM4 signal measurements and tighter tolerances to PCIe electrical test requirements [5]:

#### 1. Signal Integrity Concerns:

- PAM4, while doubling the data rate per clock cycle, introduces more signal states (four levels) than NRZ (two levels). This increased complexity makes the signal more susceptible to noise and jitter.

- b. The reduced voltage swing between PAM4 levels makes the signal more vulnerable to errors, as it requires higher precision in signal transmission and reception.

#### 2. Channel Loss Sensitivity:

- a. Although PAM4 has half the Nyquist frequency of NRZ (which can help with channel loss), the smaller signal levels and higher data rates increase the overall sensitivity to channel conditions.

- b. Channel loss budgets become increasingly critical at the higher frequencies associated with PCIe Gen6 and Gen7 (32 GHz and beyond).

#### 3. Need for Sophisticated Equalization:

- a. Implementing PAM4 signaling requires advanced equalization techniques at both the transmitter and receiver ends to compensate for signal distortion and maintain signal quality.

- b. These equalization techniques add complexity to the design and verification process.

#### 4. Transition from NRZ:

- a. The transition from the traditional Non-Return-to-Zero (NRZ) encoding to PAM4 requires significant changes in the physical layer design.

- b. Systems need to support NRZ and PAM4 concurrently during the transition phase to ensure backward compatibility, adding further complexity to the design.

#### 5. Verification Complexity:

- a. Verifying PAM4 signaling is more complex than verifying NRZ due to increased signal levels and the need for precise equalization.

- b. Extensive testing is required to ensure signal integrity under various channel conditions and noise scenarios.

Fig. 2: NRZ signal with one eye per UI, left, and PAM4 signal with three eyes, right [5]

#### Challenges associated with Flow Control Units (FLITs) [6]:

#### 1. New Format and Encoding:

- a. PCIe Gen6 introduced FLITs as a new data transfer unit, replacing previous generations' Transaction Layer Packets (TLPs). This shift requires a complete change in how data is structured, encoded, and transmitted.

- b. FLITs have a fixed size (256 bytes), different from the variable-length TLPs. This change impacts how transactions are packetized and managed.

c. New header formats and fields are introduced within FLITs, increasing the complexity of protocol handling and requiring extensive verification.

#### 2. Increased Verification Complexity:

- The new FLIT format and encoding schemes necessitate thorough verification to ensure correct operation. All possible combinations of fields and values within the FLIT must be tested.

- b. Verifying the correct handling of FLIT boundaries, especially when TLPs are split across multiple FLITs or multiple TLPs are packed into a single FLIT, adds complexity.

- c. Ensuring proper sequencing and ordering of FLITs is critical. Sequencing errors can lead to data corruption or system failures.

#### 3. Sequence Number and Retry Mechanisms:

- a. FLITs introduce new sequence numbers and retry mechanisms essential for reliable data transfer. Verifying these mechanisms is complex and requires testing various scenarios, including:

- b. Correct sequence number generation and tracking.

- c. Proper handling of acknowledgments (ACKs) and negative acknowledgments (NAKs).

- d. Accurate retransmission of FLITs in case of errors or NAKs.

- e. The "IMPLICIT\_RX\_FLIT\_SEQ\_NUM" rule, where the sequence number is not explicitly carried in the FLIT, relies on internal logic and requires careful verification.

#### 4. TX Retry Buffer Management:

- a. The transmitter (TX) must buffer FLITs if a retry is requested. It is crucial to ensure that the TX retry buffer is correctly managed.

- b. For FLITs containing multiple TLPs or split TLPs, the retry mechanism must ensure that the correct data is retransmitted without duplication or loss.

#### 5. Standard Nak/Selective Nak Handling:

- a. PCIe Gen6/Gen7 introduces Standard Nak and Selective Nak mechanisms for retrying specific FLITs.

- b. Verifying the correct handling of these Naks by both the transmitter and receiver is essential.

- c. Since the decision to send Standard Nak or Selective Nak can be implementationspecific, it adds another layer of complexity to verification.

#### 6. Interaction with Other Features:

- a. FLITs interact with new PCIe Gen6/Gen7 features, such as PAM4 signaling, Forward Error Correction (FEC), and new power states (L0p). Verifying these interactions and ensuring they function correctly is a significant challenge.

- b. For example, ensuring that FEC works correctly with the fixed-size FLIT structure and that power state transitions do not disrupt FLIT transmission requires careful verification.

As also revealed in PCI-SIG's extensive research on PCIe 6.0 implementations, FLIT mode presents substantial verification challenges due to its fundamental shift in data transfer methodology. Their technical analysis highlights that integrating FLITs with PAM4 signaling creates a unique verification scenario, requiring specialized test methodologies to ensure reliable operation across diverse system configurations. The fixed-size FLIT structure introduces specific verification requirements for ensuring data integrity when handling the complex interaction between the link layer and transaction layer [6].

| Description |               | Lane     |          |          |          |          |          |          |          |          |          |             |                     |             |             |             |             |

|-------------|---------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-------------|---------------------|-------------|-------------|-------------|-------------|

|             |               | 0        | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9        | 10          | 11                  | 12          | 13          | 14          | 15          |

|             |               | 0        | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9        | 10          | 11                  | 12          | 13          | 14          | 15          |

|             |               | 16       | 17       | 18       |          | 20       | 21       | 22       | 23       | 24       |          | 26          | 27                  |             | 29          | 30          | 31          |

|             |               | 32       | 33       | 34       | 35       | 36       |          | 38       | 39       |          | 41       | 42          | 43                  | 44          | 45          |             | 47          |

|             |               | 48       | 49       | 50       | 51       | 52       | 53       | 54       |          | 56       | 57       |             | 59                  | 60          |             | 62          | 63          |

|             |               | 64       | 65       | 66       | 67       | 68       | 69       |          | 71       | 72       | 73       | 74          | 75                  |             | 77          | 78          | 79          |

|             |               | 80       | 81       | 82       | 83       | 84       |          | 86       | 87       |          | 89       | 90          |                     | 92          | 93          | 94          | 95          |

|             | TLP Bytes     | 96       | 97       | 98       | 99       | 100      | 101      | 102      | 103      | 104      | 105      | 106         | 107                 | 108         | 109         | 110         | 111         |

| 16          | [0223]        | 112      | 113      | 114      | 115      | 116      | 117      | 118      | 119      | 120      | 121      | 122         | 123                 | 124         | 125         | 126         | 127         |

| Symbol      |               | 128      | 129      | 130      | 131      | 132      | 133      | 134      | 135      | 136      | 137      | 138         | 139                 | 140         | 141         | 142         | 143         |

| times       |               | 144      | 145      | 146      | 147      | 148      | 149      | 150      | 151      | 152      | 153      | 154         | 155                 | 156         | 157         | 158         | 159         |

|             |               | 160      | 161      | 162      | 163      | 164      | 165      | 166      | 167      | 168      | 169      | 170         | 171                 | 172         | 173         | 174         | 175         |

|             |               | 176      | 177      | 178      | 179      | 180      | 181      | 182      | 183      | 184      | 185      | 186         | 187                 | 188         | 189         | 190         | 191         |

|             |               | 192      | 193      | 194      | 195      | 196      | 197      | 198      | 199      | 200      | 201      | 202         | 203                 | 204         | 205         | 206         | 207         |

|             |               | 208      | 209      | 210      | 211      | 212      | 213      | 214      | 215      | 216      | 217      | 218         | 219                 | 220         | 221         | 222         | 223         |

|             | TLP, DLP      | 224      | 225      | 226      | 227      | 228      | 229      | 230      | 231      | 232      | 233      | 234         | 235                 | DLP<br>O    | DLP<br>1    | DLP<br>2    | DLP<br>3    |

|             | DLP, CRC, ECC | dlp<br>4 | dlp<br>5 | CRC<br>0 | CRC<br>1 | crc<br>2 | crc<br>3 | CRC<br>4 | CRC<br>5 | CRC<br>6 | CRC<br>7 | ECC1<br>[0] | <u>в</u> сс2<br>[0] | всс0<br>[0] | ECC1<br>[1] | ECC2<br>[1] | ECC0<br>[1] |

Fig. 3: Flit Layout in a x16 Link [20]

#### Challenges associated with Forward Error Correction (FEC) [7]:

#### 1. Complexity of Implementation:

- a. FEC algorithms are inherently complex and require intricate logic to implement correctly. The sophistication of the FEC scheme used increases this complexity.

- b. It is a significant challenge to ensure that the FEC encoder and decoder are implemented accurately on both the transmitter and receiver sides.

#### 2. Verification Overhead:

- a. Verifying FEC functionality requires extensive testing. All possible error patterns and scenarios must be covered to ensure the FEC can effectively correct errors.

- b. Error injection test cases with randomized symbol locations are needed to validate the FEC implementation thoroughly.

- c. Verifying the interaction between FEC and other PCIe features, such as FLITs, adds another layer of complexity to the verification process.

#### **3.** Latency Considerations:

- a. FEC processing introduces latency in the data path. The complexity of the FEC algorithm directly affects the latency.

- Balancing error correction capability with latency requirements is a challenge. More powerful FEC schemes can correct more errors but typically introduce higher latency.

- c. Minimizing FEC latency is crucial in high-speed systems like PCIe Gen6/Gen7, where even small latencies can impact performance.

#### 4. Trade-offs and Optimization:

- a. A trade-off exists between the error correction level, the amount of overhead (additional bits used for FEC), and the latency introduced.

- b. Optimizing these trade-offs to achieve the desired level of error protection without significantly impacting performance is a challenge.

- c. Factors such as the channel's expected bit error rate (BER) the application's performance requirements must be considered.

#### 5. Impact on Data Throughput:

- a. FEC adds overhead to the transmitted data, as extra bits are used for error correction information. This reduces the effective data throughput.

- b. Designers must balance the need for error correction with the impact on data throughput.

#### 6. Adaptation and Flexibility:

- a. Depending on the channel conditions, adapting the FEC scheme to provide optimal error protection may be necessary.

- b. Implementing adaptive FEC that can adjust to changing channel conditions adds complexity to the design.

Synopsys's comprehensive research on PCIe 6.0 verification also revealed that FEC implementation presents substantial verification challenges that extend beyond traditional CRC-based error detection. Their technical analysis emphasizes that thorough verification of FEC requires specialized methodologies to ensure proper correction of symbol errors introduced by PAM4 signaling. The research highlights the critical importance of comprehensive error injection techniques to validate FEC functionality across various operating conditions and error patterns. [7].

#### Challenges associated with L0p Low-Power State [8] [9] [10]:

#### 1. Verification Complexity:

- a. Correct Implementation: Verifying the correct implementation of the L0p state itself is a challenge. This includes ensuring that the state is entered and exited according to the PCIe specifications.

- b. Transitions and Sequencing: Ensuring proper transitions and sequencing between the L0p state and other power states (like L0, L1, etc.) is crucial. Incorrect transitions can lead to data corruption, system instability, or performance issues.

- c. Maintaining Data Integrity: When transitioning to or from the L0p state, it is vital to verify that data integrity is maintained. Any loss or corruption of data during power state changes can have severe consequences.

#### 2. Latency and Performance:

- a. Minimizing Latency: One key challenge is to minimize the latency associated with entering and exiting the L0p state. While L0p is designed to save power, excessive latency during transitions can negatively impact system performance. This is particularly critical at high data rates (64.0 GT/s and beyond), where small delays can accumulate and cause significant stalls.

- b. Power-Performance Trade-offs: When dealing with low-power states, there is often a trade-off between power efficiency and performance. Optimizing the L0p state to maximize power savings without sacrificing too much performance is a significant challenge.

#### **3.** Interaction with Other Features:

editor@iaeme.com

- a. Integration with Other Protocol Features: L0p state operation must be verified with other PCIe features, such as PAM4 signaling, FLITs, Forward Error Correction (FEC), Skew and different SKIP OS lengths. Ensuring these features function correctly during L0p state entry, exit, and operation is complex.

- b. System-Level Interactions: It is essential to verify how the L0p state interacts with other components and subsystems within a larger system. This includes testing for potential side effects or conflicts arising from power state transitions.

#### 4. Debugging Challenges:

- a. Identifying Issues: Debugging issues related to the L0p state can be challenging, as these issues may be intermittent or dependent on specific traffic patterns and operating conditions.

- b. Complex Scenarios: Simulating and testing all possible scenarios related to L0p state transitions and interactions can be very complex and time-consuming.

Rambus's detailed analysis of PCIe 6.0 power management revealed that L0p implementation introduces substantial verification challenges due to its dynamic power adjustment capabilities. Their research emphasizes that L0p state transitions must be carefully validated to ensure proper interaction with FLIT mode, particularly during high-bandwidth data transfers [8]. Additionally, Synopsys's technical bulletin highlights the critical balance between power efficiency and latency in HPC applications, noting that L0p verification requires comprehensive testing across diverse traffic patterns to ensure optimal performance [9]. Further insights from PCI-SIG's official documentation emphasize that L0p introduces sophisticated power state control mechanisms that demand rigorous verification to maintain data integrity during state transitions, especially in systems operating at 64.0 GT/s and above data rate [10].

#### Challenges associated with optimizing channel performance [11] [12][13]:

#### 1. Maintaining Signal Integrity at Higher Frequencies:

- a. The operating frequencies also rise as data rates increase (up to 64.0 GT/s in Gen6 and 128.0 GT/s in Gen7). This makes the signals more susceptible to noise, jitter, and attenuation.

- b. Maintaining signal integrity becomes paramount. Any degradation in signal quality can lead to bit errors and unreliable data transmission.

#### 2. Channel Loss Management:

- a. Signal loss in the transmission channel increases at higher frequencies. This loss must be carefully managed through proper material selection, trace design, and connector choice.

- b. The channel loss budget becomes tighter, requiring precise engineering to ensure signals can travel the required distance without excessive degradation.

#### 3. Impedance Control:

- Maintaining a consistent impedance along the entire signal path is critical. Impedance mismatches can cause signal reflections, leading to signal distortion and errors.

- b. Achieving accurate impedance control becomes more challenging at higher frequencies, requiring advanced manufacturing techniques and careful layout design.

#### 4. Jitter Management:

- a. Jitter (variations in signal timing) can severely impact data transmission at high speeds. Sources of jitter include clock instability, signal reflections, and crosstalk.

- Managing and minimizing jitter is essential to ensure reliable data transmission. This requires careful clock design, signal path optimization, and noise reduction techniques.

#### 5. Crosstalk Reduction:

- a. Crosstalk (interference between adjacent signal lines) becomes more concerning as signal density increases. Crosstalk can corrupt signals and lead to errors.

- b. Reducing crosstalk requires careful layout planning, including proper signal spacing, shielding, and the use of ground planes.

#### 6. Equalization Techniques:

- a. Advanced equalization techniques are required at both the transmitter and receiver ends to compensate for channel loss and signal distortion.

- b. Designing and implementing effective equalization circuits adds complexity to the design process and requires careful optimization.

#### 7. Physical Design Constraints:

- a. Optimizing channel performance often involves trade-offs with other design constraints, such as cost, power consumption, and form factor.

- b. Balancing these trade-offs and finding an optimal solution can be challenging.

#### 8. Verification and Testing:

- a. Verifying channel performance at high frequencies requires sophisticated measurement equipment and techniques.

- b. Testing for signal integrity, jitter, and crosstalk under various operating conditions can be time-consuming and complex.

Signal Integrity Journal's comprehensive analysis revealed that the transition from PCIe Gen6 to Gen7 introduces unprecedented signal integrity challenges, particularly as data rates double from 64.0 GT/s to 128.0 GT/s. Their technical assessment emphasizes that channel design must account for significantly higher frequency content, requiring advanced materials with lower dielectric losses and sophisticated simulation methodologies [11]. Further insights from Synopsys highlight that end-to-end verification solutions must address the complex interplay between equalization, channel characteristics, and compliance requirements to ensure reliable operation at these extreme data rates [12]. Additional research from Synopsys experts Sanyal and Olvera indicates that PCIe 7.0's bandwidth demands for AI applications necessitate new approaches to channel design, with specialized attention to crosstalk mitigation and jitter control techniques to maintain signal integrity across increasingly dense interconnect architectures [13].

#### Challenges associated with maintaining backward compatibility [14][15]:

#### 1. Increased Design Complexity:

- a. Supporting Multiple Generations: To ensure backward compatibility, PCIe Gen6 and Gen7 designs must support the latest specifications and all previous generations (Gen1, Gen2, Gen3, Gen4, and Gen5). This requires including logic and features for handling the older protocols, even if they are not used in the most advanced systems.

- b. Mixed Environments: Systems often have components from different PCIe generations. Devices with Gen6/Gen7 capabilities must be able to seamlessly communicate with older devices, requiring careful management of data rates, signaling, and protocols.

#### 2. Verification Challenges:

a. Extensive Regression Testing: Ensuring backward compatibility necessitates extensive regression testing with devices and systems from previous PCIe generations. This involves setting up diverse test environments and running various test cases.

- b. Compatibility Matrix: Verification engineers must create and maintain a comprehensive compatibility matrix to track which features and functions are compatible with each generation. This adds to the complexity of test planning and execution.

- c. Legacy Protocols: Thoroughly testing legacy protocols and ensuring their proper interaction with new features introduced in Gen6/Gen7 is challenging. This requires expertise in both the older and newer PCIe specifications.

#### 3. Physical Layer Compatibility:

- a. Signaling Differences: Different PCIe generations may use different signaling techniques (e.g., NRZ in earlier generations vs. PAM4 in Gen6/Gen7). Hardware must be designed to accommodate these differences and switch between them as needed.

- b. Connector Compatibility: While the physical connectors generally remain the same, ensuring electrical compatibility at high speeds across different generations is difficult. This involves addressing impedance matching, signal integrity, and timing differences.

#### 4. Power Management Compatibility:

- a. Power State Transitions: Older PCIe generations might use different power states and management schemes. Gen6/Gen7 systems must handle power state transitions correctly when communicating with older devices, ensuring stability and data integrity.

- b. Maintaining Performance:

- c. The overhead of Compatibility Logic: Supporting legacy protocols can introduce overhead in the design, potentially impacting performance, even when communicating with other Gen6/Gen7 devices. Designers must minimize this overhead to maintain optimal performance.

#### 5. Documentation and Support:

- a. Legacy Documentation: Maintaining documentation for all supported PCIe generations adds to the burden of engineering teams.

- b. Technical Support: Providing technical support for legacy devices and addressing compatibility issues can be complex and time-consuming.

Wander's detailed analysis in Signal Integrity Journal revealed that physical compatibility challenges are particularly pronounced when transitioning from PCIe Gen6 to Gen7, with the CEM connector facing significant challenges at 128.0 GT/s data rates. His

research highlights that maintaining backward compatibility while pushing performance boundaries requires sophisticated connector design and signal integrity techniques to ensure reliable operation across multiple generations [14]. Further insights from Ruggles and Sanyal at Synopsys emphasize that comprehensive end-to-end design solutions are essential for addressing backward compatibility challenges, particularly when implementing the dual-mode PAM4/NRZ signaling required for Gen6 and beyond. Their technical assessment underscores the importance of verification methodologies that can effectively validate multi-generational compatibility without compromising the performance benefits of newer implementations [15].

#### 4. Solutions to Key Challenges in Verifying High-Speed PCIe Implementations

#### I. Solutions for Challenges Associated with Pulse Amplitude Modulation 4 (PAM4):

- **1. Signal Integrity Concerns:**

- Advanced Signal Conditioning: Employ advanced signal conditioning techniques at the transmitter and receiver, including pre-emphasis, de-emphasis, and adaptive equalization. This helps compensate for signal distortions and improve signal quality.

- Noise Filtering and Shielding: Implement robust noise filtering circuits and shielding to minimize the impact of external noise and interference on the PAM4 signals.

- Jitter Reduction Techniques: To minimize signal timing variations, utilize low-jitter clock sources and implement jitter cleaning circuits.

#### 2. Channel Loss Sensitivity:

- **Optimized Channel Design:** Carefully design the physical channels with low-loss materials, optimized trace geometries, and controlled impedance to minimize signal loss at high frequencies.

- **Signal Repeaters and Retimers:** Employ repeaters and Retimers to regenerate and clean up the PAM4 signals at strategic points in the channel, extending the reach and improving signal integrity.

#### 3. Need for Sophisticated Equalization:

- Adaptive Equalization: Implement adaptive equalization at the receiver that can dynamically adjust the equalization parameters based on the received signal quality, compensating for channel variations and distortions.

- **Pre-distortion at the Transmitter:** Use pre-distortion techniques at the transmitter to pre-compensate for known channel distortions, improving the signal quality at the receiver.

#### 4. Transition from NRZ:

- **Dual-Mode Support:** Design systems with dual-mode support, allowing them to operate in NRZ and PAM4 modes. This ensures backward compatibility and a smooth transition to PAM4.

- Mode Detection and Switching: Implement logic to automatically detect the signaling mode of connected devices and seamlessly switch between NRZ and PAM4 modes.

#### **5. Verification Complexity:**

- **Comprehensive Test Suites:** Develop comprehensive test suites that cover all possible PAM4 signal levels, transitions, and channel conditions.

- Error Injection and Analysis: Utilize error injection techniques to simulate various error scenarios and verify the effectiveness of error detection and correction mechanisms. Employ advanced analysis tools to identify and characterize errors.

#### **II.** Solutions for Challenges Associated with Flow Control Units (FLITs):

#### **1. New Format and Encoding:**

- **Detailed Specification Analysis:** Thoroughly analyze and understand the FLIT format and encoding rules defined in the PCIe Gen6/Gen7 specifications.

- **Model Development:** Develop accurate and detailed models of the FLIT structure and encoding schemes for simulation and verification.

#### 2. Increased Verification Complexity:

- **Constraint Random Testing:** Utilize constraint random testing to generate a wide range of valid and invalid FLIT sequences and combinations of fields.

- **Coverage-Driven Verification:** Implement a robust coverage model that tracks all possible FLIT configurations and ensures that all scenarios are tested.

- Assertion-Based Verification: Use assertions to check for protocol violations and ensure that FLITs are handled correctly.

#### 3. Sequence Number and Retry Mechanisms:

- Sequence Number Tracking: Implement logic to track sequence numbers and verify their correctness accurately.

- ACK/NAK Handling Verification: Develop test cases to verify the correct handling of ACKs and NAKs for FLIT retransmission.

- **Retry Mechanism Testing:** Thoroughly test the retry mechanism under various error scenarios, including single and multiple FLIT retries.

#### 4. TX Retry Buffer Management:

- **Buffer Sizing and Management:** Ensure the TX retry buffer is adequately sized and managed correctly to avoid data loss or corruption during retransmissions.

- **Data Integrity Checks:** Implement data integrity checks to verify that retried FLITs contain the correct data and that no data is lost or duplicated.

#### 5. Standard Nak/Selective Nak Handling:

- Nak Logic Verification: Verify the correct implementation of Standard Nak and Selective Nak logic in both the transmitter and receiver.

- Selective Nak Test Cases: Develop specific test cases to verify the selective Nak functionality, including requests for retransmission of individual FLITs.

### 6. Interaction with Other Features:

- **Integrated Testing:** To ensure correct interactions, perform integrated testing of FLITs with other PCIe features, such as PAM4, FEC, and power states.

- **Cross-Feature Coverage:** Develop a coverage model that ensures all combinations of FLITs with other features are tested.

#### III. Solutions for Challenges Associated with Forward Error Correction (FEC):

#### **1.** Complexity of Implementation:

- **Modular Design:** A modular design approach breaks down the complex FEC logic into smaller, more manageable blocks, simplifying implementation and verification.

- Code Reviews and Validation: Conduct thorough code reviews and simulations to validate the correctness of the FEC encoder and decoder.

#### 2. Verification Overhead:

- Error Injection Campaigns: Conduct extensive error injection campaigns to test the FEC's ability to correct various error patterns.

- **Randomized Error Testing:** Use randomized error patterns and locations to ensure comprehensive FEC testing.

- **Statistical Analysis:** Perform statistical analysis of error correction results to evaluate the effectiveness of the FEC scheme.

#### **3. Latency Considerations:**

- **Pipeline Optimization:** Optimize the FEC pipeline to minimize latency.

- **Trade-off Analysis:** Carefully analyze FEC strength and latency trade-offs to find the optimal balance.

#### 4. Trade-offs and Optimization:

- Adaptive FEC: Implement adaptive FEC that can dynamically adjust the FEC scheme based on channel conditions and BER requirements.

- **Performance Monitoring:** Monitor the BER and adjust the FEC scheme to maintain the desired error rate.

#### **5. Impact on Data Throughput:**

- **Overhead Reduction:** Optimize the FEC overhead by choosing efficient encoding schemes and minimizing the number of redundant bits.

- **Throughput Analysis:** Analyze the impact of FEC overhead on data throughput and adjust as needed to meet performance requirements.

#### 6. Adaptation and Flexibility:

- **Dynamic Configuration:** Allow for dynamic configuration of the FEC scheme based on channel conditions or application requirements.

- **Real-time Adaptation:** Implement real-time adaptation of the FEC scheme based on feedback from the channel.

#### IV. Solutions for Challenges Associated with L0p Low-Power State:

#### **1. Verification Complexity:**

- **State Machine Verification:** Develop a detailed state machine model of the L0p state and verify its transitions using formal verification techniques.

- **Transition Coverage:** Ensure comprehensive coverage of all possible transitions into and out of the L0p state.

#### 2. Latency and Performance:

- Latency Measurement: Accurately measure the latency associated with L0p state transitions and optimize the transition times.

- **Power Management Unit (PMU) Simulation:** Simulate the PMU behavior to verify its impact on L0p state transitions and overall performance.

#### **3. Interaction with Other Features:**

- **Integrated Power and Protocol Testing:** Conduct integrated power management testing with other PCIe features (PAM4, FLITs, FEC) to ensure seamless operation.

- **Power State Assertion:** Use assertions to verify the correct power state during transitions and operations.

#### 4. Debugging Challenges:

• **Debug Visibility:** Enhance debug visibility into power state transitions and related events.

• **Trace and Log Analysis:** Utilize trace and log analysis tools to identify and debug L0p state issues.

#### V. Solutions for Challenges Associated with Optimizing Channel Performance:

#### 1. Maintaining Signal Integrity at Higher Frequencies:

- Advanced Materials and Design: Use high-quality materials and advanced design techniques to minimize signal loss and reflections at high frequencies.

- **Electromagnetic Simulations:** Perform detailed electromagnetic simulations to analyze and optimize signal integrity.

#### 2. Channel Loss Management:

- Loss Budget Analysis: Conduct a comprehensive loss budget analysis to ensure the channel meets the required performance targets.

- **Material Selection:** Select materials with low dielectric loss and high conductivity to minimize signal attenuation.

#### 3. Impedance Control:

- **Impedance Modeling and Simulation:** Use impedance modeling and simulation tools to optimize trace widths and spacing for consistent impedance.

- **Manufacturing Control:** Implement strict manufacturing controls to ensure accurate and consistent impedance.

#### 4. Jitter Management:

- **Clocking Design:** Design a low-jitter clocking system with minimal phase noise.

- Jitter Analysis Tools: Use jitter analysis tools to identify and mitigate sources of jitter.

- 5. Crosstalk Reduction:

- Layout Optimization: Optimize the layout to minimize crosstalk, including proper signal spacing, shielding, and ground plane design.

- **Crosstalk Simulation:** Perform crosstalk simulations to identify and address potential issues.

- Advanced Equalizer Design: Design and implement advanced equalizer circuits (e.g., Continuous-Time Linear Equalizers (CTLE), Decision Feedback Equalizers (DFE)) to adapt to varying channel conditions and minimize signal distortion.

- **Optimization Algorithms:** Employ optimization algorithms to fine-tune equalizer parameters for optimal performance.

#### 6. Physical Design Constraints:

- **Co-design and Trade-off Analysis:** Perform a thorough co-design process involving electrical, mechanical, and thermal considerations to balance performance, cost, power consumption, and form factor constraints.

- **Design Optimization Tools:** Utilize design optimization tools and methodologies to explore the design space and identify optimal solutions.

#### 7. Verification and Testing:

- Advanced Measurement Techniques: Employ sophisticated measurement equipment (e.g., Vector Network Analyzers (VNA), oscilloscopes with high bandwidth) to characterize channel performance at high frequencies accurately.

- Simulation and Modeling Correlation: Ensure that simulation and modeling results are closely correlated with actual measurements to validate the design's accuracy and identify any discrepancies.

- **Comprehensive Test Suites:** Develop comprehensive test suites to cover all relevant signal integrity parameters (e.g., insertion loss, return loss, jitter, crosstalk) under various operating conditions and corner cases.

#### VI. Solutions for Challenges Associated with Maintaining Backward Compatibility:

#### 1. Increased Design Complexity:

- Modular Design with Isolation: Implement a modular design approach with welldefined interfaces and isolation mechanisms to separate the logic for different PCIe generations. This allows for easier management and modification of specific design parts without impacting others.

- **Parameterizable and Configurable Blocks:** Use parameterizable and configurable blocks in the design to adapt to different PCIe generations. This allows for reusing core logic while adjusting parameters based on each generation's requirements.

- **Software-Defined Configuration:** Use software-defined configuration to enable dynamic switching between different PCIe generations. Based on the connected devices, firmware or software can control this.

#### 2. Verification Challenges:

- Automated Regression Testing: Develop an automated regression testing framework to run many test cases for all supported PCIe generations. This ensures that changes in the design do not inadvertently break backward compatibility.

- **Comprehensive Compatibility Matrix:** Create and maintain a detailed compatibility matrix that lists all supported features and their compatibility with different PCIe generations. This matrix should be regularly updated and used to guide test planning.

- Legacy Test Suites and Equipment: Maintain legacy test suites and equipment to test older PCIe generations. This can be crucial for verifying compatibility with older devices and systems.

- Interoperability Testing: Conduct extensive interoperability testing with devices from different vendors and various PCIe generations to ensure seamless communication and compatibility.

#### 3. Physical Layer Compatibility:

- **Multi-Mode Transceivers:** Design transceivers that support multiple signaling techniques (NRZ and PAM4) and can dynamically switch between them. This requires careful design of the analog front-end and clocking circuits.

- Adaptive Equalization for Different Signaling: Implement adaptive equalization that can adjust parameters based on the signaling technique (NRZ or PAM4). This ensures optimal signal quality for all generations.

- **Connector and Cable Qualification:** Qualify connectors and cables for compatibility with all supported PCIe generations. This includes electrical testing to ensure impedance matching and signal integrity at various data rates.

#### 4. Power Management Compatibility:

- **Power State Management Logic:** Design power management logic to correctly handle power state transitions for all supported PCIe generations. This may require maintaining separate power management modules for older generations.

- **Power State Transition Testing:** Develop test cases to verify the correct behavior of power state transitions for all combinations of PCIe generations in the system.

#### 5. Maintaining Performance:

- **Optimize Compatibility Logic:** Optimize the compatibility logic to minimize overhead and ensure that it does not significantly impact performance when communicating with devices of the same generation.

- **Performance Monitoring:** Monitor system performance when communicating with devices from different PCIe generations to identify bottlenecks or performance degradation.

#### 6. Documentation and Support:

• **Comprehensive Documentation:** Maintain comprehensive documentation for all supported PCIe generations, including technical specifications, design guidelines, and troubleshooting information.

- **Technical Support Expertise:** Ensure technical support teams have the expertise to assist customers with backward compatibility issues.

- **Knowledge Base:** Create a knowledge base of common backward compatibility issues and solutions to help customers and support teams resolve problems quickly.

These solutions address the challenges of verifying high-speed PCIe implementations, focusing on PAM4, FLITs, FEC, L0p, channel performance, and backward compatibility. Implementing these solutions will contribute to more reliable and efficient PCIe systems.

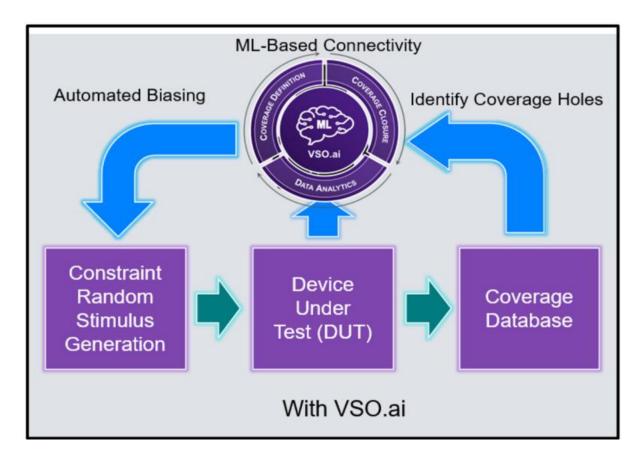

#### 5. Future Trends: AI-Driven Approaches for Enhanced PCIe Verification

As the complexity of PCIe technology escalates with each generation, traditional verification methods face significant challenges. Integrating artificial intelligence (AI) and machine learning (ML) techniques into PCIe verification workflows is becoming essential to address these. AI/ML offers the potential to automate and optimize various aspects of the verification process, thereby enhancing efficiency, accuracy, and overall system reliability. Integrating AI and machine learning technologies is transforming the future of PCIe verification, particularly in achieving functional coverage closure and optimizing test methodologies. Research by Nolan demonstrates that AI-driven verification approaches using UVM can reduce overall verification time by up to 45% while improving coverage metrics by an average of 35% [16]. Implementing machine learning algorithms in test generation has shown promise, with neural network-based approaches achieving 92% accuracy in predicting high-risk coverage holes that require additional testing focus [16].

Furthermore, the industry is seeing advancements in AI-driven tools specifically designed for verification. For instance, Synopsys VSO.ai is an AI-powered solution that optimizes semiconductor chip verification. It includes a Coverage Inference Engine to help define coverage points based on simulated stimulus and the RTL design. VSO.ai uses connectivity engines and a machine learning-based solver to target hard-to-hit coverage points. Features like test grading, unreachability analysis, and Intelligent Coverage Optimization (ICO) enhance test diversity using reinforcement learning, resulting in faster regression turnaround time, higher coverage closure, and discovery of more design and testbench bugs. NVIDIA's experience with Synopsys tools, including VSO.ai, has shown significant improvements, such as 33% more functional coverage in the same number of tests run and a 5X reduction in the size of the regression test suite, underscoring the potential of AI to revolutionize verification workflows [17].

Fig. 4: The Benefits of VSO.ai [19]

Inspired by these successful applications of AI/ML in optimizing UVM-based semiconductor design verification and specific tools like Synopsys VSO.ai, we propose the following AI-driven approaches to augment PCIe verification further:

#### 1. Intelligent Test Case Generation

Traditional PCIe test case generation often involves random or manually crafted tests, which can be time-consuming and may not effectively cover critical scenarios. Drawing from the principles of Reinforcement Learning (RL) used in the UVM optimization study and tools like VSO.ai, we can develop AI models to generate targeted test cases for PCIe interfaces automatically. These models can learn from historical verification data and specification documents to identify test scenarios that maximize coverage and expose potential vulnerabilities. By focusing on critical areas and edge cases, AI-driven test generation can significantly reduce the number of redundant tests, thereby saving simulation time and computational resources. The application of AI in PCIe verification. Studies indicate that machine learning models trained on historical verification data can achieve up to 88% accuracy

in predicting potential compliance violations before they manifest in hardware. This predictive capability has proven especially valuable in verifying complex protocol interactions, with automated test generation systems demonstrating the ability to create targeted test scenarios that achieve 95% coverage of corner cases with 40% fewer test cases than traditional methods [18].

#### 2. Test Case Prioritization Using Predictive Analytics

Managing and prioritizing numerous test cases is a significant challenge in large-scale PCIe verification. Inspired by predictive analytics models in the UVM study and the strategies used by VSO.ai, we can employ machine learning algorithms to prioritize test cases based on their likelihood of detecting bugs. These models can identify patterns that indicate high-risk test scenarios by analyzing historical verification data, design changes, and code coverage reports. Supervised learning algorithms can be trained to rank test cases, ensuring that those with a higher probability of revealing errors are executed first. This approach accelerates bug discovery and optimizes resource allocation, leading to faster verification cycles. For PCIe, critical transactions or sequences that are more prone to errors due to high-speed signaling or complex protocol interactions can be prioritized for early testing.

#### 3. Automated Bug Detection and Classification

Analyzing PCIe simulation results manually can be labor-intensive and error-prone, especially at higher data rates where vast amounts of data are generated. Adapting the deep learning techniques used for UVM bug detection and the anomaly detection capabilities of VSO.ai, we can develop AI models to automate the analysis of PCIe simulation logs. These models can be trained to recognize anomalies, protocol violations, and timing issues that may indicate design flaws. Using pattern recognition and anomaly detection algorithms, AI can quickly sift through simulation data, identifying discrepancies that traditional methods might miss. Moreover, based on the nature of the discrepancies, the models can be trained to classify bugs, such as signal integrity issues, protocol errors, or power management failures. Low-power verification has emerged as a critical focus area where AI-driven methodologies show promise. Research by Amelia reveals that machine learning algorithms can optimize power-aware verification strategies, reducing the time required for power-related coverage closure by up to 60%. The integration of AI-assisted debugging tools has demonstrated significant improvements in root cause analysis, with automated systems capable of identifying powerrelated issues with 94% accuracy while reducing debug time by approximately 55% compared to conventional approaches [18]. This automated bug detection and classification process can significantly reduce debugging time and improve the overall efficiency of PCIe verification.

#### 4. Adaptive Verification Environments

Building on the concept of autonomous verification systems in the UVM study and the dynamic adjustment capabilities of VSO.ai, future PCIe verification environments can leverage AI to become more adaptive and self-optimizing. These systems can continuously learn from previous verification cycles, adapting to new design architectures and optimizing test strategies in real-time. Reinforcement learning can be used to explore edge cases that are difficult to reach through random testing, ensuring comprehensive coverage. Furthermore, AI can dynamically adjust verification parameters based on real-time feedback from simulations or hardware measurements. For instance, if the AI detects a high error rate in a particular part of the PCIe link, it can automatically increase the intensity of testing in that area or adjust the test environment to simulate real-world conditions better.

#### 5. Hybrid AI-Human Models with Explainable AI (XAI)

Recognizing the importance of human expertise in critical design areas, we propose using hybrid AI-human models for PCIe verification, aligning with VSO.ai's approach to augment rather than replace human engineers. While AI can handle the bulk of automated testing and analysis, human engineers can provide critical judgment, context, and oversight, particularly for complex or safety-critical applications. Explainable AI (XAI) techniques can be integrated into the verification process to foster trust and transparency. XAI can provide insights into the decision-making processes of AI models, allowing engineers to understand why certain test cases were generated or specific bugs were flagged. This transparency is crucial for building confidence in AI-driven verification, especially in automotive and highperformance computing sectors, where reliability and safety are paramount.

#### Conclusion

The landscape of PCIe verification has undergone a significant transformation, driven by technological advancements and increasing system complexity. Integrating Artificial Intelligence (AI) and Machine Learning (ML) technologies is no longer optional but essential, revolutionizing verification methodologies and enabling more efficient test generation, improved coverage metrics, and enhanced defect detection capabilities. The successful implementation of targeted compliance verification methods demonstrates the industry's ability to address growing debugging and validation efficiency challenges, significantly reducing debugging time by up to 45% and improving coverage metrics by 35%, as demonstrated by Nolan's research.

#### Deepak Kumar Lnu

As PCIe technology continues to evolve, with Gen7 delivering unprecedented data rates of 128 GT/s per lane, the verification complexity continues to increase. This evolution necessitates sophisticated verification frameworks that can address the unique challenges posed by features such as PAM4 signaling, FLIT-based transactions, Forward Error Correction (FEC), and low-power states like L0p. Adopting AI-driven verification tools and methodologies, combined with innovative approaches to compliance testing, is crucial for ensuring the reliability and performance of these advanced systems.

Moreover, AI/ML plays a pivotal role in optimizing test methodologies. Machine learning algorithms, particularly neural network-based approaches, have shown remarkable success, achieving 92% accuracy in predicting high-risk coverage holes. Predictive analytics models trained on historical verification data can achieve up to 88% accuracy in anticipating potential compliance violations, significantly reducing the risk of hardware failures. In complex protocol interactions, automated test generation systems using AI have demonstrated the ability to achieve 95% coverage of corner cases with 40% fewer test cases than traditional methods.

The benefits of AI/ML extend to low-power verification as well. Research indicates that machine learning algorithms can optimize power-aware verification strategies, reducing the time required for power-related coverage closure by up to 60%. AI-assisted debugging tools have shown significant improvements in root cause analysis, with automated systems identifying power-related issues with 94% accuracy while reducing debug time by approximately 55%.

Integrating AI-driven techniques is poised to reshape the landscape of PCIe verification, driving unprecedented levels of efficiency, accuracy, and automation. As semiconductor designs grow in complexity, the need for intelligent, adaptive, and scalable verification methodologies will become increasingly critical. The future of UVM-based verification will likely be defined by the deeper integration of advanced AI technologies, which will address current limitations and open new possibilities for optimizing verification. This includes developing autonomous verification systems, hybrid AI-human models, AI-powered predictive analytics, and cloud-based AI verification, essential for ensuring robust operation in safety-critical applications and high-performance computing environments.

In conclusion, applying AI to PCIe verification presents a powerful approach to optimizing test generation, prioritization, and bug detection. The observed efficiency gains and accuracy improvements underscore the potential for AI to transform traditional verification processes. Future research should aim to refine these models for broader applicability and explore ways to enhance model interpretability, ultimately paving the way for fully automated

and intelligent verification environments. This will enable the industry to meet the verification challenges of next-generation PCIe implementations while maintaining backward compatibility and reliability standards.

#### References

- [1] Technavio, "PCI Express Market to Grow by USD 53.74 Billion from 2024-2028, Driven by PCIE Integration with IEEE 1394 (FireWire) and AI's Role in Market Transformation," PRNewswire, Sep 30, 2024. [Online]. Available: https://www.prnewswire.com/news-releases/pci-express-market-to-grow-by-usd-53-74-billion-from-2024-2028--driven-by-pcie-integration-with-ieee-1394-firewire-andais-role-in-market-transformation---technavio-302262036.html

- [2] Aditi Sharma, "Industry's First Verification IP for PCIe 7.0," Synopsys Blogs, Jun 13, 2024. [Online]. Available: https://www.synopsys.com/blogs/chip-design/industry-first-vip-for-pcie-7-0.html

- [3] Anubhav Mangla, "The Evolution of PCI Express: From Gen1 to Gen6 and Beyond," ResearchGate, February 2025. [Online]. Available: https://www.researchgate.net/publication/388802882\_THE\_EVOLUTION\_OF\_PCI\_ EXPRESS\_FROM\_GEN1\_TO\_GEN6\_AND\_BEYOND

- [4] Fidus, "Exploring PCIe Generation 6.0 Advancements & Benefits," 2 May 2024.

[Online]. Available: https://fidus.com/blog/exploring-pcie-gen-6-advancementsbenefits/

- [5] TeledyneLecroy, "PAM4 on PCIe 6 Electrical Testing," 2024. Available: https://www.teledynelecroy.com/doc/pam4onpcie6-electrical-testing

- [6] PCI-SIG, "PCIe 6.0 Specification Webinar Q&A: Deeper Dive into FLIT Mode, PAM4, and Forward Error Correction," 2024. Available: https://pcisig.com/blog/pcie%C2%AE-60-specification-webinar-qa-deeper-dive-flitmode-pam4-and-forward-error-correction-fec

- [7] Synopsys, "PCIe 6 Verification: FEC & CRC," 2024. Available: https://www.synopsys.com/blogs/chip-design/pcie-6-verifaction-fec-crc.html

- [8] Rambus, "Revolutionizing Power Efficiency in PCIe 6.x: L0p and FLIT Mode in Action," 2024. Available: https://www.rambus.com/blogs/revolutionizing-powerefficiency-in-pcie-6x-10p-and-flit-mode-in-action/

- [9] Madhumita Sanyal, "Navigating PCIe 6.0 Power and Latency Challenges in HPC SoCs"

Synopsys. Available: https://www.synopsys.com/designware-ip/technicalbulletin/pcie-6-hpc-socs.html

- [10] Debendra Das Sharma, "The PCIe® 6.0 Specification Webinar Q&A: Leveling Up with L0p," PCI-SIG. Available: https://pcisig.com/pcie%C2%AE-60-specification-webinarqa-leveling-l0p

- [11] Signal Integrity Journal, "Navigating Signal Integrity Challenges: Transitioning from PCIe Gen6 to Gen7," 2024. Available: https://www.signalintegrityjournal.com/articles/3462-navigating-signal-integritychallenges-transitioning-from-pcie-gen6-to-gen7

- [12] Synopsys, "How to Maximize PCIe 6 with End-to-End Design Solutions," 2024. Available: https://www.synopsys.com/blogs/chip-design/how-to-maximize-pcie-6with-end-to-end-design-solutions.html

- [13] Madhumita Sanyal and Monica Olvera, "How PCIe 7.0 Addresses AI's Bandwidth Demands," Synopsys. https://www.synopsys.com/designware-ip/technicalbulletin/pcie-7-design-ai-bandwidth.html

- [14] Abhijit Wander, "Navigating Signal Integrity Challenges: Transitioning from PCIe Gen6 to Gen7," Signal Integrity, February 21, 2024. https://www.signalintegrityjournal.com/articles/3462-navigating-signal-integritychallenges-transitioning-from-pcie-gen6-togen7#:~:text=The%20CEM%20connector%20faces%20a,integrate%20with%20previ ous%20PCIe%20generations.

- [15] Gary Ruggles, Madhumita Sanyal, "How to Maximize PCIe 6.0's Advantages with Endto-End PCIe Design Solutions," Synopsys, Jun 16, 2023. https://www.synopsys.com/blogs/chip-design/how-to-maximize-pcie-6-with-end-toend-design-solutions.html#3

- [16] Jasmin Nolan, "AI-Driven Approaches for Optimizing Semiconductor Design Verification Using UVM," ResearchGate, October 2024. [Online]. Available:

https://www.researchgate.net/publication/384480064\_AI-Driven\_Approaches\_for\_Optimizing\_Semiconductor\_Design\_Verification\_Using\_UV M

- [17] Taruna Reddy, "Reducing Manual Effort and Achieving Better Chip Verification Coverage with AI and Formal Techniques," Synopsys, Sep 04, 2024. https://www.synopsys.com/blogs/chip-design/vso-ai-nvidia.html

- [18] Oscar Amelia, "AI-Driven Testing and Validation Techniques for Low-Power Semiconductor Design Verification Using UVM," ResearchGate, October 2024.

[Online]. Available: https://www.researchgate.net/publication/384896673\_AI-Driven\_Testing\_and\_Validation\_Techniques\_for\_Low-Power\_Semiconductor\_Design\_Verification\_Using\_UVM

- [19] Mike Gianfagna, "AMD Puts Synopsys AI Verification Tools to the Test," SemiWiki, 08-28-2023. Available: https://semiwiki.com/eda/synopsys/333623-amd-putssynopsys-ai-verification-tools-to-the-test/

- [20] PCI-SIG, "The PCIe 7.0 Specification, Version 0.7 is Now Available to Members." Available: https://pcisig.com/specifications/pcie-70-specification-version-07-nowavailable-members

**Citation:** Deepak Kumar Lnu. (2025). PCIe Verification at High Speeds: Challenges, Solutions, and Future Trends. International Journal of Computer Engineering and Technology (IJCET), 16(1), 3987-4016.

Abstract Link: https://iaeme.com/Home/article\_id/IJCET\_16\_01\_274

#### Article Link:

https://iaeme.com/MasterAdmin/Journal\_uploads/IJCET/VOLUME\_16\_ISSUE\_1/IJCET\_16\_01\_274.pdf

**Copyright:** © 2025 Authors. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

This work is licensed under a Creative Commons Attribution 4.0 International License (CC BY 4.0).

4016

☑ editor@iaeme.com